# **CHAPTER 5. CIRCUIT DESCRIPTION**

# [1] Circuit description

# 1. General description

In this machine, the facsimile control block except the printer control is mainly composed of the units shown in Fig. 1.

# 2. PWB configuration AC CORD POWER SUPPLY PWB LINE LINE CIS UNIT PRINTER PRINTER PWB OPERATION PANEL PWB OPERATION PANEL PWB Fig. 1

# 1) Control PWB

The control PWB controls all the other operations except the printing operation of the printer.

# 2) LIU PWB

The LIU PWB controls the I/F telephone function of the circuit with the control signals from the control PWB.

# 3) CIS UNIT

CIS UNIT converts the image of the sending or copying draft into the photoelectric signals and transmits the signals to the control PWB.

# 4) Operation panel PWB

The operation panel PWB detects the key input, turns on and off LED and displays LCD according to the control signals from the control PWB.

# 5) Power supply PWB

DC voltages (+5V, +24V) are produced from AC120V, and are supplied to the printer unit and control PWB unit.

# 6) PC I/F PWB (Option: FO-47IF)

An interface to PC is done by IEEE1284, and image data (bitmap) from PC are outputted to the printer.

# 7) Memory PWB

The 2MByte image memory composed by flash memory which can be supported. When FO-3MK (OPTION) installed, a capacity rise is possible to 5 MByte.

# [2] Circuit description of control PWB

# 1. General description

The control PWB is composed of the following blocks.

- Main control block

- ② Image memory block

- 3 Modem block

- ④ Image signal process block

- ⑤ Speaker amplifier

- 6 Reading process and mechanical control block

- 7 Gate array (A) block

- ODEC block

- Page memory block

- ① Drive block

- JBIG block

### 2. Description of each block

# (1) Main control block

The main control block uses RISC microprocessor HD6437021 as CPU, being composed of ROM (2 MByte), DRAM (2 MByte) and SRAM (256 KByte).

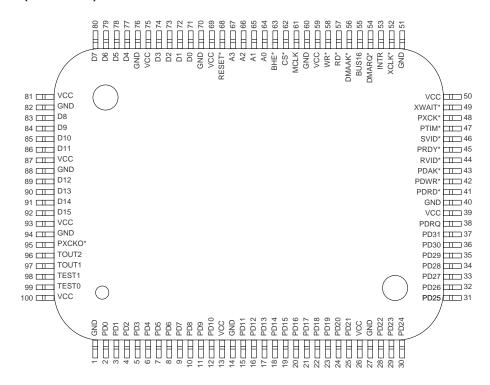

# 1) SH7021 (IC27): pin-100, QFP (main CPU)

The device is a microprocessor which integrates the peripheral functions, using CPU of 32-bit RISC type as the core. In the instrument, the following peripheral functions are mainly used.

- ① ROM of 32 KByte and RAM of 1 KByte are integrated. A part of programs are stored in the integrated ROM.

- ② DMA controller (4 channels are provided, and 2 channels alone are used.)

- ch.0: Used to transmit image data between CODEC (HD813201F) and DRAM (IC16).

- ch.2: Used to transmit image data between Flash memory (option) and DRAM(IC16).

- ③ Clock-synchronous type serial communication interface commands and statuses are communicated with PCU.

- 4 Interruption

IRQ4, IRQ7: Interruption request from gate array (A) (LZ9FJ59)

IRQ6: Interruption request from gate array (B) (LR38292)

IRQ0, IRQ1, IRQ2, IRQ3, IRQ5, IRQ7 : Not used.

NMI: Not used.

⑤ DRAM controller

MHz.

Addressing to DRAM(IC16) of the system and control and refresh control of  $\overline{RAS}$  and  $\overline{CAS}$  signals are executed.

- 6 Timer and watch dog timer

- ⑦ General-purpose I/O port Control of Liu and control of analog process of read signals are

- executed.

8 Clock oscillation

Crystal oscillator of 19.66 MHz is connected for operation of 19.66

- 9 Generation of alarm sound and ringer sound

The keys on the operation panel are pressed to respectively generate the key input sound, alarm sound and ringer sound.

### 2) 27C160 (IC4): pin-42, DIP (EPROM)

Programs are stored in a 16 Mbit ROM.

### 3) HY5118164 or MSM5118165 (IC16): pin-42, SOJ (DRAM)

Used as the system memory of main CPU and transmission buffer of communication.

# 4) SM8578BV (IC30): pin-8, SOP (Real time clock IC)

It is oscillated with the quartz oscillator of 32.768 kHz, and the clock and calendar functions are provided. Even if the power supply of the main body is turned off, it is backed up with lithium battery. This device executes the clock-synchronous type serial communication with the gate array (A), and CPU can know the time and date through the gate array (A).

# SH7021 (IC27) Terminal descriptions

| Classification         | Code          | Terminal No.<br>(TFP-100B)               | I/O | Name                                       | Function                                                                                                                                                                                                                                         |

|------------------------|---------------|------------------------------------------|-----|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                  | Vcc           | 13, 38, 63,<br>73, 80, 88                | I   | Power                                      | Connect to the power supply.  Connect Vcc terminals to the power units of all systems.  If any open terminal is present, it will not operate                                                                                                     |

|                        | Vss           | 4,15,24,32,<br>41,50,59,70,<br>81,82, 92 | I   | Ground                                     | Connect to the ground. Connect Vcc terminals to the power units of all systems. If any open terminal is present, it will not operate.                                                                                                            |

| Clock                  | EXTAL         | 71                                       | I   | External clock                             | Connect to the quartz oscillator. Moreover, EXTAL terminal can input the external clock.  Use the same frequency for the quartz oscillator, external clock and system clock.                                                                     |

|                        | XTAL          | 72                                       | I   | Crystal                                    | Connect the quartz oscillator. Connect the same frequency of the system clock (CK).  To input external clock from EXTAL terminal, open EXTAL terminal.                                                                                           |

|                        | СК            | 69                                       | 0   | System clock                               | Supply system clock to the peripheral device.                                                                                                                                                                                                    |

| System control         | RES           | 76                                       | I   | Reset                                      | If this terminal is turned to the low level when NMI is at the high level, it will be brought into the power-on state. If this terminal is turned to the low level when NMI is at the low level, it will be brought into the manual.reset state. |

|                        | WDTOVF        | 75                                       | 0   | Watch dog timer overflow                   | It is overflow output signal from WDT.                                                                                                                                                                                                           |

|                        | BREQ          | 60                                       | I   | Bus right request                          | Select the low level to make the external device request the release of bus right.                                                                                                                                                               |

|                        | BACK          | 58                                       | 0   | Bus right request acknowledge              | It indicates that the bus right is released to the external device.  When receiving BACK signal, the device which outputs BREQ signal can know that bus right is obtained.                                                                       |

| Operation mode control | MD2~<br>MD0   | 79~77                                    | I   | Mode setting                               | The terminal determines the operation mode.  During operation, don't vary any input value. The relationship between MD2 thru MD0 and operation modes are shown in the following list.                                                            |

| Interrupt              | NMI           | 74                                       | I   | No-maskable interrupt                      | This is the interrupt request terminal which can not be masked.  Either leading edge or trailing edge is selected for receiving.                                                                                                                 |

|                        | IRQ0~<br>IRQ7 | 65,66,67,68,<br>97,98,99,100             | I   | Interrupt request 0 thru 7                 | This is the interrupt request terminal which can be masked. Either level input or edge input can be selected.                                                                                                                                    |

|                        | IRQOUT        | 61                                       | 0   | Interrupt request output in the slave mode | It indicates that a factor of interrupt occurs. It indicates that interrupt occurs in the bus release mode.                                                                                                                                      |

| Address                | A21~A0        | 45~42,40,39,<br>37~33,31~25,<br>23~20    | 0   | Address                                    | Address is output.                                                                                                                                                                                                                               |

| Data bus               | AD15~<br>AD0  | 19~16,14,<br>12~5,3~1                    | I/O | Data bus                                   | Bidirectional data bus of 16 bits Multiplex is possible with the low-order 16 bits of the address.                                                                                                                                               |

|                        | DPH           | 64                                       | I/O | High-order side data bus parity            | Parity data corresponds to D15 thru D8.                                                                                                                                                                                                          |

|                        | DPL           | 62                                       | I/O | Low-order side data bus parity             | Parity data corresponds to D7 thru D0.                                                                                                                                                                                                           |

Relationship between MD2 thru MD0 and operation modes

(Continuing)

| Relationship | between M | DZ thru MDt | operation modes |                |                     |  |

|--------------|-----------|-------------|-----------------|----------------|---------------------|--|

| MD2          | MD1       | MD0         | Operation mode  | Integrated ROM | Bus width of area 0 |  |

| 0            | 0         | 0           |                 | Invalid        | 8-bit size          |  |

| 0            | 0         | 1           | MCU mode        | iiivaliu       | 16-bit size         |  |

| 0            | 1         | 0           |                 | Valid          | _                   |  |

| 0            | 1         | 1           | (Reserved)      | _              | _                   |  |

| 1            | 0         | 0           | (Reserved)      | _              | _                   |  |

| 1            | 0         | 1           | (Reserved)      | _              | _                   |  |

| 1            | 1         | 0           | (Reserved)      | (Reserved) —   |                     |  |

| 1            | 1         | 1           | (Reserved) — —  |                | _                   |  |

# SH7021 (IC27) Terminal descriptions

| Classification                     | Code              | Terminal No.<br>(TFP-100B) | I/O | Name                                                    | Function                                                                                             |

|------------------------------------|-------------------|----------------------------|-----|---------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Bus control                        | WAIT              | 54                         | I   | Wait                                                    | It is input to insert Tw into the bus cycle during access to the external space.                     |

|                                    | RAS               | 52                         | 0   | Low address strobe                                      | Timing signal of low address strobe of DRAM                                                          |

|                                    | CASH              | 47                         | 0   | High-order column address strobe                        | Timing signal of column address strobe of DRAM It is output for access to high-order 8 bits of data. |

|                                    | CASL              | 49                         | 0   | Low-order column address strobe                         | Timing signal of column address strobe of DRAM It is output for access to low-order 8 bits of data.  |

|                                    | RD                | 57                         | 0   | Read                                                    | It indicates that outside is read out.                                                               |

|                                    | WRH               | 56                         | 0   | High-order write                                        | It indicates writing at the external high-order 8 bits.                                              |

|                                    | WRL               | 55                         | 0   | Low-order write                                         | It indicates writing at the external low-order 8 bits.                                               |

|                                    | CS0~CS7           | 46~49,<br>51~54            | 0   | Chip select 0 thru 7                                    | Chip select signal for external memory or device                                                     |

|                                    | ĀĦ                | 61                         | 0   | Address hold                                            | Address hold timing signal for device which uses multiplex bus of address/data                       |

|                                    | HBS,<br>LBS       | 20<br>56                   | 0   | Low-/high-order byte strobe                             | Strobe signal of high/low byte (Commonly used with AO, WRH.)                                         |

|                                    | WR                | 55                         | 0   | Write                                                   | Output during writing. (Commonly used with WRL.)                                                     |

| DMAC                               | DREQ0,<br>DREQ1   | 66,68                      | I   | DMA transfer request (Channels 0 and 1)                 | Input terminal of DMA transfer request from external                                                 |

|                                    | DACK0,<br>DACK1   | 65,67                      | 0   | DMA transfer request<br>receiving (Channels<br>0 and 1) | It indicates that DMA transfer request is received.                                                  |

| 16-bit integrated timer pulse unit | TIOCA0,<br>TIOCB0 | 51,<br>53                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 0)     | Output terminal of input capture input/output conveyor                                               |

| (ITU)                              | TIOCA1,<br>TIOCB1 | 62,<br>64                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 1)     | Output terminal of input capture input/output conveyor                                               |

|                                    | TIOCA2,<br>TIOCB2 | 83,<br>84                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 2)     | Output terminal of input capture input/output conveyor                                               |

|                                    | TIOCA3,<br>TIOCB3 | 85,<br>86                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 3)     | Output terminal of input capture input/output conveyor                                               |

|                                    | TIOCA4,<br>TIOCB4 | 87,<br>89                  | I/O | ITU input<br>capture/output<br>conveyor (Channel 4)     | Output terminal of input capture input/output conveyor                                               |

|                                    | TOCXA4,<br>TOCXB4 | 90,<br>91                  | 0   | ITU output conveyor (Channel 4)                         | Output terminal of output conveyor                                                                   |

|                                    | TCLKA~<br>TCLKD   | 65,66,90,<br>91            | I   | ITU timer clock input                                   | External clock input terminal to counter of ITU                                                      |

| Timing pattern controller (TPC)    | TP15~<br>TP0      | 100~93,<br>91~89,<br>87~83 | 0   | Timing pattern<br>Output 15 thru 0                      | Output terminal of timing pattern                                                                    |

| Serial communication               | TxD0,<br>TxD1     | 94,<br>96                  | 0   | Sending data<br>(Channels 0 and 1                       | Sending data output terminal of SCI0, 1                                                              |

| nterface (SCI)                     | RxD0,<br>RxD1     | 93,<br>95                  | I   | Receiving data (Channels 0 and 1)                       | Receiving data input terminal of SCI0, 1                                                             |

|                                    | SCK0,<br>SCK1     | 97,<br>98                  | I/O | Serial clock<br>(Channels 0 and 1)                      | Clock input/output terminal of SCI0, 1                                                               |

| I/O port                           | PA15~<br>PA0      | 68~64,<br>62~60,<br>58~51  | I/O | Port A                                                  | Input/output terminal of 16 bits Input/output can be assigned for each bit.                          |

|                                    | PB15~<br>PB0      | 100~93,<br>91~89,<br>87~83 | I/O | Port B                                                  | Input/output terminal of 16 bits Input/output can be assigned for each bit.                          |

# (2) Image memory block

This block is composed of memory PWB circult. Refer to [2'] Circuit description of memory PWB for the details.

# (3) Modem block

The block is mainly composed of the modem R288F (IC41), and is provided with the following modem function.

Table 1-1. Configurations, Signaling Rates, and Data Rates

|                 |              | Carrier Frequency | Data Rate (bps) | Symbol Rate    | Bits/Symbol - | Bits/Symbol - | Constellation |

|-----------------|--------------|-------------------|-----------------|----------------|---------------|---------------|---------------|

| Configuration   | Modulation 1 | (Hz) $\pm$ 0.01%  | ± 0.01%         | (Symbols/Sec.) | Data          | TCM           | Points        |

| V. 34 33600 TCM | TCM          | Note 2            | 33600           | 3429 only      | Note 2        | Note 2        | Note 2        |

| V. 34 31200 TCM | TCM          | Note 2            | 31200           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 28800 TCM | TCM          | Note 2            | 28800           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 26400 TCM | TCM          | Note 2            | 26400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 24000 TCM | TCM          | Note 2            | 24000           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 21600 TCM | TCM          | Note 2            | 21600           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 19200 TCM | TCM          | Note 2            | 19200           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 16800 TCM | TCM          | Note 2            | 16800           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 14400 TCM | TCM          | Note 2            | 14400           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 12000 TCM | TCM          | Note 2            | 12000           | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 9600 TCM  | TCM          | Note 2            | 9600            | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 7200 TCM  | TCM          | Note 2            | 7200            | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 4800 TCM  | TCM          | Note 2            | 4800            | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 34 2400 TCM  | TCM          | Note 2            | 2400            | Note 2         | Note 2        | Note 2        | Note 2        |

| V. 23 1200/75   | FSK          | 1700/420          | 1200/75         | 1200           | 1             | 0             | _             |

| V. 21           | FSK          | 1080/1750         | 0-300           | 300            | 1             | 0             | _             |

| V. 17 14400 TCM | TCM          | 1800              | 14400           | 2400           | 6             | 1             | 128           |

| V. 17 12000 TCM | TCM          | 1800              | 12000           | 2400           | 5             | 1             | 64            |

| V. 17 9600 TCM  | TCM          | 1800              | 9600            | 2400           | 4             | 1             | 32            |

| V. 7200 TCM     | TCM          | 1800              | 7200            | 2400           | 3             | 1             | 16            |

| V. 29 9600      | QAM          | 1700              | 9600            | 2400           | 4             | 0             | 16            |

| V. 29 7200      | QAM          | 1700              | 7200            | 2400           | 3             | 0             | 8             |

| V. 29 4800      | QAM          | 1700              | 4800            | 2400           | 2             | 0             | 4             |

| V. 27 4800      | DPSK         | 1800              | 4800            | 1600           | 3             | 0             | 8             |

| V. 27 2400      | DPSK         | 1800              | 2400            | 1200           | 2             | 0             | 4             |

| V. 21 Channel 2 | FSK          | 1750              | 300             | 300            | 1             | 0             | _             |

# Notes:

1. Modulation legend: TCM: Trellis-Coded Modulation QAM: Quadrature Amplitude Modulation

FSK: Frequency Shift Keying DPSK: Differential Phase Shift Keying

2. Adaptive; established during handshake:

|                    | Carrier Fre       | quency (Hz)       |

|--------------------|-------------------|-------------------|

| Symbol Rate (Baud) | V. 34 Low Carrier | V.34 High Carrier |

| 2400               | 1600              | 1800              |

| 2800               | 1680              | 1867              |

| 3000               | 1800              | 2000              |

| 3200               | 1829              | 1920              |

| 3429               | 1959              | 1959              |

Table 2-1. MDP Pin Signals -68- Pin PLCC

| Pin | Signal Label  | I/O Type | Interface 3               | Pin | Signal Label | I/O Type | Interface                |

|-----|---------------|----------|---------------------------|-----|--------------|----------|--------------------------|

| 1   | NC            |          | NC                        | 35  | RXD          | OA       | DTE Serial Interface     |

| 2   | NC            | _        | _                         | 36  | VDD2         | PWR      |                          |

| 3   | NC            | _        | _                         | 37  | -CTS         | OA       | DTE Serial Interface     |

| 4   | NC            | _        | _                         | 38  | NC           | _        | _                        |

| 5   | -RI/TXRQ      | OA       | DTE Serial/DMA Interface  | 39  | NC           | _        | _                        |

| 6   | RINGD         | IA       | LIU: RINGD                | 40  | DGND3        | GND      | _                        |

| 7   | -RTS          | IA       | DTE serial Interface      | 41  | VDD3         | PWR      | _                        |

| 8   | IRQ           | OA       | Host Parallel Interface   | 42  | NC           | _        | _                        |

| 9   | D1            | IA/OB    | Host Parallel Interface   | 43  | DGND4        | GND      | _                        |

| 10  | DGND1         | GND      |                           | 44  | NC           | _        | _                        |

| 11  | VDD1          | PWR      |                           | 45  | NC           | _        | _                        |

| 12  | XTLI          | I        | Crystal/Clock Circuit     | 46  | EYESYNC      | OA       | Eye Pattern Test Circuit |

| 13  | XTLO          | 0        | Crystal/Clock Circuit     | 47  | -EYECLK      | OA       | Eye Pattern Test Circuit |

| 14  | D0            | IA/OB    | Host Parallel Interface   | 48  | EYEXY        | OA       | Eye Pattern Test Circuit |

| 15  | D2            | IA/OB    | Host Parallel Interface   | 49  | NC           | _        | _                        |

| 16  | D3            | IA/OB    | Host Parallel Interface   | 50  | TDCLK        | OA       | DTE Serial Interface     |

| 17  | D5            | IA/OB    | Host Parallel Interface   | 51  | -RLSD        | OA       | DTE Serial Interface     |

| 18  | D7            | IA/OB    | Host Parallel Interface   | 52  | -RDCLK       | OA       | DTE Serial Interface     |

| 19  | DGND2         | GND      |                           | 53  | GP0          | MI       | MDP: EYESYNC             |

| 20  | RS0           | IA       | Host Parallel Interface   | 54  | XTCLK        | IA       | DTE Serial Interface     |

| 21  | 5VA           | PWR      |                           | 55  | DGND5        | GND      |                          |

| 22  | AGND1         | GND      |                           | 56  | VDD4         | PWR      |                          |

| 23  | RIN           | I(DA)    | Line Interface            | 57  | TXD          | IA       | DTE Serial Interface     |

| 24  | VC            | MI       | To GND through capacitors | 58  | -DSR/RXRQ    | OA       | DTE Serial/DMA Interface |

| 25  | VREF          | MI       | To VC through capacitors  | 59  | -RESET       | OA       | Host Parallel Interface  |

| 26  | TXA2          | O (DD)   | Line Interface            | 60  | -READ        | IA       | Host Parallel Interface  |

| 27  | TXA1          | O (DD)   | Line Interface            | 61  | -WRITE       | IA       | Host Parallel Interface  |

| 28  | -TALK (-RLYB) | OA       | Line Interface            | 62  | -CS          | IA       | Host Parallel Interface  |

| 29  | SPKR          | O (DF)   | Speaker Circuit           | 63  | RS4          | IA       | Host Parallel Interface  |

| 30  | AGND2         | GND      |                           | 64  | RS3          | IA       | Host Parallel Interface  |

| 31  | -OHRC (-RLYA) | OD       | Line Interface            | 65  | RS2          | IA       | Host Parallel Interface  |

| 32  | -POR          | MI       | MDP: -RESET               | 66  | RS1          | IA       | Host Parallel Interface  |

| 33  | NC            | _        | _                         | 67  | D6           | IA/OB    | Host Parallel Interface  |

| 34  | -DTR          | IA       | DTE Serial Interface      | 68  | D4           | IA/OB    | Host Parallel Interface  |

# Notes:

1. I/O types:

MI= Modem interconnect.

IA, IB= Digital input

OA, OB = Digital output

I (DA) = Analog input

O (DD), O (DF) = Analog output

2. NC= No external connection allowed

3. Interface Legend:

MDP = Modem Data Pump

DTE = Data Terminal Equipment

The above functions are controlled by getting an access to the interface memory in the modem through the data bus from CPU (IC27) of the control PWB. The interface memory is composed of 32 8-bit registers, and is controlled with the bank switch. Accordingly, the register is selected by the register selection signals (RS4 to RS0) of 5 bits and chip selection signal (CS). The major content controlled by these registers is as follows.

### 1) Configuration register

Mode setting of V34, V17, V29, V27, G2, FSK and tone transmission.

### 2) Option register

Equalizing method of equalizer, carrier detection threshold, addition of echo suppressor protect tone, and setting of transmission/reception mode.

# 3) Others

G2AGC control, tone frequency setting, and so on.

Moreover, data is read from these registers through the data bus to monitor the statuses of the modem such as tone detection, training pattern detection and so on.

Next, transmission/reception operation is described.

During sending, the sent data is given from the control block to the modem through the data bus. Then, it is modulated and sent to LIU PWB with SIGTX signal. During receiving, the received data is sent from LIU PWB to the modem with SIGRX signal and is demodulated. Then, it is sent to the control block with the data bus. The above operation is done with the modem LSI (IC).

# (4) Image signal process block

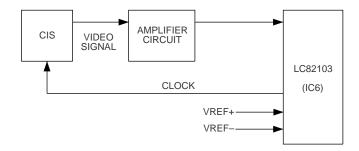

Fig. 2

The CIS is driven by the LSI (LC82103), and the output video signal from the CIS is input into the LC82103 through the amplifying circuit. The ADC and buffer are provided in the LC82103, and the digital image processing is performed.

# (5) Speaker amplifier

The speaker amplifier monitors the line under the on-hook mode, outputs the buzzer sound generated from the SH7021, ringer sound, DTMF generated from the modem, and line sound.

# (6) Reading process and mechanical control block

### 1) Mechanical control block

The mechanical control block is mainly composed of the gate array (A) (IC17: LZ9FJ59) to control the following.

### (a) Sending motor control

The revolution speed and timing of the sending motor are controlled to output the control signals to the motor driver (IC7).

# (b) End stamp and LED lamp control

On/off of the end stamp and LED lamp is controlled with the software.

# (7) Gate array (A) block

This block is mainly composed of the gate array (A) (IC17: LZ9FJ59), and has the following functions.

- Mapper

- Mapping is executed in the memory area of the memories, gate array (B), modem, CODEC and reading process LSI (LC82103).

- ② Mechanical control block Refer to 1) Mechanical control block of 2-6 Reading and mechanical control block.

- ③ IC interface for clock Writing and reading to IC (IC30: SM8578BV) for clock is executed in the clock-synchronous type serial transfer mode.

- (4) LIU control port

- ⑤ PC interface

- Control of PC I/F Asic (FO-47IF)

# LC82103 (IC6)

|   |        |   | Туре        |    |             |

|---|--------|---|-------------|----|-------------|

| 1 | INPUT  | В | BIDIRECTION | NC | NOT CONNECT |

| 0 | OUTPUT | Р | POWER       |    |             |

| PIN | I/O      | Name        | Function                                    | PIN | I/O | Name     | Function                                 |

|-----|----------|-------------|---------------------------------------------|-----|-----|----------|------------------------------------------|

| 1   | В        | D7          |                                             | 43  | Р   | AVDD     | Analog system power supply pin.          |

| 2   | В        | D6          |                                             | 44  | - 1 | DALRH    | D/A converter high reference voltage pin |

| 3   | В        | D5          | CPU interface data bus pin                  |     |     |          | for A/D converter low reference voltage. |

| 4   | В        | D4          | D7 is the MSB pin, and D0 is the            | 45  | 0   | ATAPL    | D/A converter monitor signal output pin  |

| 5   | В        | D3          | LSB pin.                                    |     |     |          | for A/D converter low reference voltage. |

| 6   | В        | D2          |                                             | 46  | Р   | AGND     | Analog system ground pin.                |

| 7   | В        | D1          | <b>-</b>                                    | 47  | В   | PD7/SD   | DMA output pin/serial data output pin    |

| 8   | В        | D0          |                                             | 48  | В   | PD6/SDCK | DMA output pin/serial data               |

| 9   | Р        | DGND        | Digital system ground pin.                  |     |     |          | transmission clock pin.                  |

| 10  | Р        | DVDD        | Digital system power supply pin.            | 49  | Р   | DGND     | Digital system ground pin.               |

| 11  | ı        | A8          |                                             | 50  | В   | PD5/SDE  | DMAoutput pin/serial date                |

| 12  | ı        | A7          |                                             |     |     |          |                                          |

| 13  | ı        | A6          | CPU interface address bus pin               | 51  | В   | PD4/PP4  |                                          |

| 14  | ı        | A5          | A12 is the MSB pin, and A0 is the LSB pin.  | 52  | В   | PD3/PP3  | DMA output pin/general-purpose           |

| 15  | ı        | A4          | LOB piri.                                   | 53  | В   | PD2/PP2  | I/O port pin.                            |

| 16  | 1        | A3          |                                             | 54  | В   | PD1/PP1  |                                          |

| 17  | Р        | DGND        | Digital system ground pin.                  | 55  | В   | PD0/PP0  |                                          |

| 18  | 1        | A2          | 3 7 0 1                                     | 56  | Р   | DVDD     | Digital system power supply pin.         |

| 19  | 1        | A1          | CPU interface address bus pin.              | 57  | В   | DACK/PP5 | DMA data acknowledge signal input        |

| 20  | i        | A0          | <u> </u>                                    |     |     |          | pin/general-purpose I/O port pin.        |

| 21  | 1        | WR          | CPU interface write signal pin.             | 58  | В   | DREQ/PP6 | DMA data request signal output           |

| 22  | i        | RD          | CPU interface read signal pin.              |     |     |          | pin/ general-purpose I/O port pin.       |

| 23  | i        | A12         | CPU interface address bus pin.              | 59  | В   | MTP/PP7  | Moter drive timing signal output         |

| 24  | P        | DVDD        | Digital system power supply pin.            |     | _   |          | nin/ general-nurnose I/O nort nin        |

| 25  | i        | CLKIN       | System clock input pin.                     | 60  | 0   | CLK2     | Sensor drive timing signal output        |

| 26  | i        | A11         | Cyclom clock input piin                     | 61  | 0   | CLK1     | pin.                                     |

| 27  | i        | A10         | CPU interface address bus pin.              | 62  | 0   | RS       |                                          |

| 28  | i        | A9          |                                             | 63  | 0   | SH       |                                          |

| 29  | i        | CS          | CPU interface chip select signal pin.       | 64  | P   | DGND     | Digital system ground pin.               |

| 30  | i        | ICLK        | External sampling point signal input pin.   |     | -   |          | - ισιοι - γ στοι - σ στοι - σ μ στοι - σ |

| 31  | i        | TRIG        | External trigger signal input pin.          |     |     |          |                                          |

| 32  | i        | RESET       | System reset pin.                           |     |     |          |                                          |

| 33  | 0        | SAMP/LININT | A/D converter sampling point monitor        |     |     |          |                                          |

|     |          | J ,         | signal output pin/LINE signal output pin.   |     |     |          |                                          |

| 34  | ı        | TEST        | Test pin (Connect to ground in normal use.) |     |     |          |                                          |

| 35  | i        | REF         | DRAM refresh signal input pin.              |     |     |          |                                          |

| 36  | P        | AGND        | Analog system ground pin.                   |     |     |          |                                          |

| 37  | <u>'</u> | DALRL       | D/A converter low reference voltage pin     |     |     |          |                                          |

| •   |          |             | for A/D converter low reference voltage.    |     |     |          |                                          |

| 38  | 1        | DAHRL       | D/A converter low reference voltage pin     |     |     |          |                                          |

|     |          | DATE        | for A/D converter high reference voltage.   |     |     |          |                                          |

| 39  | ı        | AIN         | Sensor signal input pin.                    |     |     |          |                                          |

| 40  | i        | TEMP        | Temperature signal input pin.               |     |     |          |                                          |

| 41  | 0        | ATAPH       | D/A converter monitor signal output pin     |     |     |          |                                          |

| 7.  |          |             | for A/D converter high reference voltage.   |     |     |          |                                          |

| 42  | 1        | DAHRH       | D/A converter high reference voltage pin    |     |     |          |                                          |

| 74  | '        | DALIKI      | for A/D converter high reference voltage.   |     |     |          |                                          |

|     |          |             | Tiol Aid converter high reference voltage.  |     |     |          |                                          |

Note: Not using the input pins must be connected to "Digital system power supply or ground".

# LZ9FJ59 (IC17) Terminal list

| PIN | I/O    | Name    | Function                                           | PIN | I/O      | Name    | Function                              |

|-----|--------|---------|----------------------------------------------------|-----|----------|---------|---------------------------------------|

| 1   | IO2M   | RTCDT   | RTC data input/output                              | 51  | IO2M     | D12     | System data input/output              |

| 2   | O2M    | RTCCK   | RTC data transfer clock                            | 52  | IO2M     | D11     | System data input/output              |

| 3   | O2M    | RTCCE   | RTC chip select                                    | 53  | IO2M     | D10     | System data input/output              |

| 4   | O2M    | RTCIO   | RTC input/output control                           | 54  | ı        | A7      | System address input                  |

| 5   | TO     | GAIN    | Output port                                        | 55  | i        | A6      | System address input                  |

| 6   | 1      | MTSTART | Input port                                         | 56  | i        | A5      | System address input                  |

| 7   | i      | LCINT   | Interrupt request signal from LC82103              | 57  | i        | A4      | System address input                  |

| 8   | O2M    | XLCCS   | Chip select signal to LC82103                      | 58  | i        | A3      | System address input                  |

| 9   | 0      | AO9     | Reading/QM-coder LSI address output                | 59  | i        | A2      | System address input                  |

| 10  | 0      | AO10    | Reading/QM-coder LSI address output                | 60  | IS       | SHCK    | Clock (19.6MHz) from CPU              |

| 11  | _      | GND     | Ground                                             | 61  | _        | GND     | Ground                                |

| 12  | 0      | AO11    | Reading/QM-coder LSI address output                | 62  | _        | VDD     | Power supply                          |

| 13  | 0      | AO12    | Reading/QM-coder LSI address output                | 63  | 1        | A1      | System address input                  |

| 14  | O2M    | XLCRD   | Read signal to LC82103                             | 64  | i        | A0      | System address input                  |

| 15  | O2M    | XLCWR   | Write signal to LC82103                            | 65  | IO2M     | D9      | System data input/output              |

| 16  | 0      | AO0     | Reading/QM-coder LSI address output                | 66  | IO2M     | D8      | System data input/output              |

| 17  | 0      | AO1     | Reading/QM-coder LSI address output                | 67  | IO2M     | D7      | System data input/output              |

| 18  | 0      | AO2     | Reading/QM-coder LSI address output                | 68  | IO2M     | D6      | System data input/output              |

| 19  | 0      | AO3     | Reading/QM-coder LSI address output                | 69  | IO2M     | D5      | System data input/output              |

| 20  | _      | VDD     | Power supply                                       | 70  | IO2M     | D4      | System data input/output              |

| 21  | _      | GND     | Ground                                             | 71  | IO2M     | D3      | System data input/output              |

| 22  | 0      | AO4     | Reading/QM-coder LSI address output                | 72  | IO2M     | D2      | System data input/output              |

| 23  | 0      | AO5     | Reading/QM-coder LSI address output                | 73  | IO2M     | D1      | System data input/output              |

| 24  | 0      | AO6     | Reading/QM-coder LSI address output                | 74  | IO2M     | D0      | System data input/output              |

| 25  | 0      | AO7     | Reading/QM-coder LSI address output                | 75  | - IOZIVI | GND     | Ground                                |

| 26  | 0      | AO8     | Reading/QM-coder LSI address output                | 76  | IS       | XRESET  | Reset signal                          |

| 27  | 0      | CRNT    | Output port                                        | 77  | O2M      | XINT7   | Interrrupt request signal to CPU      |

| 28  | _      | GND     | Ground                                             | 78  | O2M      | XINT4   | Interrrupt request signal to CPU      |

| 29  | 0      | TXB1    | B-phase current control output 1                   | 79  | O2M      | XWAIT   | Wait request signal to CPU            |

| 30  | 0      | TXB0    | B-phase current control output 0                   | 80  | I        | XRAS    | Input RAS signal from CPU             |

| 31  | 0      | TXA1    | A-phase current control output 1                   | 81  | i        | A18     | System address input                  |

| 32  | 0      | TXA0    | A-phase current control output 0                   | 82  | i        | A19     | System address input                  |

| 33  | 0      | TXPB    | B-phase current direction setting                  | 83  | i        | A20     | System address input                  |

| 34  | 0      | TXPA    | A-phase current direction setting                  | 84  | i        | A21     | System address input                  |

| 35  | ı      | A12     | System address input                               | 85  | i        | XCS2    | Chip select 2 signal input            |

| 36  | i      | A11     | System address input                               | 86  | i        | XCS6    | Chip select 6 signal input            |

| 37  | i      | A10     | System address input                               | 87  | i        | XWRL    | System write (high-order byte) signal |

| 38  | ı      | A9      | System address input                               | 88  | i        | XWRH    | System write (low-order byte) signal  |

| 39  | i      | A8      | System address input                               | 89  | i        | XRD     | System read signal                    |

| 40  | _      | GND     | Ground                                             | 90  | i        | XDACK0  | DMA acknowledge 0 input from CPU      |

| 41  | ID     | QMPDRQ  | DMA request input (QM-coder)                       | 91  | O2M      | XDREQ0  | DMA request 0 output to CPU           |

| 42  | O2M    | XQMPDAK | DMA acknowledge output (QM-coder)                  | 92  | I        | XDACK1  | DMA acknowledge 1 input from CPU      |

| 43  | ID     | QMCDRQ  | DMA request input (QM-coder)                       | 93  | O2M      | XDREQ1  | DMA request 1 output to CPU           |

| 44  | O2M    | XQMCDAK | DMA acknowledge output (QM-coder)                  | 94  | O2M      | XGABCS  | Chip select (gate array B)            |

| 45  | O2M    | XQMRD   | Read signal to QM-coder                            | 95  | O2M      | XSRAMCS | Chip select (SRAM)                    |

| 46  | O2M    | XQMWR   | Write signal to QM-coder                           | 96  | O2M      | XPGMCS  | Chip select (SKAM)                    |

| 47  | O2M    | XQMCS   | Chip select signal to QM-coder                     | 97  | I        | XMDMINT | Interrupt request signal from Modem   |

| 48  | IO2M   | D15     | System data input/output                           | 98  | O2M      | XMDMCS  | Chip select (Modem)                   |

| 49  | IO2M   | D14     | System data input/output  System data input/output | 99  | OZIVI    | XMDMRST | Modem reset output                    |

| 50  | IO2M   | D13     | System data input/output  System data input/output | 100 | _        | VDD     |                                       |

|     | IOZIVI | פוטן    | System data input/output                           | 100 |          | ן א ח   | Power supply                          |

# LZ9FJ59 (IC17) Terminal list

| PIN | I/O | Name     | Function                            | PIN | I/O  | Name     | Function                                |

|-----|-----|----------|-------------------------------------|-----|------|----------|-----------------------------------------|

| 101 | _   | GND      | Ground                              | 131 | O2M  | XD6004RD | Read signal to D6004 (PC I/F)           |

| 102 | O2M | XEXCS    | Chip select (spare)                 | 132 | O2M  | XD6004WR | Write signal to D6004 (PC I/F)          |

| 103 | I   | XCDCINT  | Interrupt request signal from CODEC | 133 | O2M  | D6004ALE | Address strobe signal to D6004 (PC I/F) |

| 104 | I   | XCDCDRQ  | DMA request signal (CODEC)          | 134 | _    | GND      | Ground                                  |

| 105 | O2M | XCDCCS   | Chip select (CODEC)                 | 135 | Ю    | AD7      | PC I/F address/data input/output        |

| 106 | 0   | XWR      | System write output                 | 136 | Ю    | AD6      | PC I/F address/data input/output        |

| 107 | O2M | FLBK4    | Bank control 4                      | 137 | Ю    | AD5      | PC I/F address/data input/output        |

| 108 | O2M | FLBK3    | Bank control 3                      | 138 | Ю    | AD4      | PC I/F address/data input/output        |

| 109 | O2M | FLBK2    | Bank control 2                      | 139 | Ю    | AD3      | PC I/F address/data input/output        |

| 110 | O2M | FLBK1    | Bank control 1                      | 140 | Ю    | AD2      | PC I/F address/data input/output        |

| 111 | IU  | XFLBSY   | Flash memory busy signal input      | 141 | _    | GND      | Ground                                  |

| 112 | IU  | FLSZ0    | Input port                          | 142 | _    | VDD      | Power supply                            |

| 113 | IU  | FLSZ1    | Input port                          | 143 | IS   | CK16M    | 16MHz clock input                       |

| 114 | O2M | XFLSTD   | Chip select (flash standard)        | 144 | ID   | TEST1    | Test terminal                           |

| 115 | O2M | XFLOPT   | Chip select (flash option)          | 145 | Ю    | AD1      | PC I/F address/data input/output        |

| 116 | IU  | XCI      | Input port                          | 146 | Ю    | AD0      | PC I/F address/data input/output        |

| 117 | IU  | XRHS     | Input port                          | 147 | IU   | XB4FRS   | Input port                              |

| 118 | IU  | XEXHS    | Input port                          | 148 | IU   | XFRSNS   | Input port                              |

| 119 | TO  | DPON     | Output port                         | 149 | IU   | XORGSNS  | Input port                              |

| 120 | _   | GND      | Ground                              | 150 | IU   | XROLSNS  | Input port                              |

| 121 | TO  | TXMUTE   | Output port                         | 151 | I    | PRTSNS1  | Input port                              |

| 122 | IU  | HSDTCT   | Input port                          | 152 | TO   | CDCMSK   | Output port                             |

| 123 | TO  | MPXC     | Output port                         | 153 | TO   | PLG0ON   | Plunger 0 control                       |

| 124 | ТО  | MPXB     | Output port                         | 154 | ТО   | PLG10N   | Plunger 1 control                       |

| 125 | TO  | DPMUTE   | Output port                         | 155 | TO   | LEDON    | CIS LED light source control            |

| 126 | IU  | PCDTCT   | Input port                          | 156 | IU   | XEXINT0  | Interrupt request signal from PC I/F    |

| 127 | ТО  | FAXPCSL  | Output port                         | 157 | IU   | XEXINT1  | Interrupt request signal (spare)        |

| 128 | O2M | XD9001CS | Chip select (PC I/F D9001)          | 158 | I    | PCIFSL   | PC I/F select signal input              |

| 129 | O2M | XD9001RW | Read signal to D9001 (PC I/F)       | 159 | IO2M | IOP0     | Input port (spare)                      |

| 130 | O2M | XD9001WR | Write signal to D9001 (PC I/F)      | 160 | _    | GND      | Ground                                  |

I : Input terminal (TTL level input)

IS : Input terminal (TTL level schmitt input)

$\begin{tabular}{ll} IU & : Input terminal (TTL level input, pull up resistor 250 K$\Omega$ building in) \\ ID & : Input terminal (TTL level input, pull down resistor 250 K$\Omega$ building in) \\ IO & : Input/output terminal (TTL level input, output electric current: IoL=4.0 mA) \\ IO2M & : Input/output terminal (TTL level input, output electric current: IoL=2.0 mA) \\ \end{tabular}$

O : Output terminal (Output electric current: I oL=4.0 mA)

O2M : Output terminal (Output electric current: I oL=2.0 mA)

TO : Try-state output terminal (Output electric current: IoL=4.0 mA)

VDD : Power supply GND : Ground

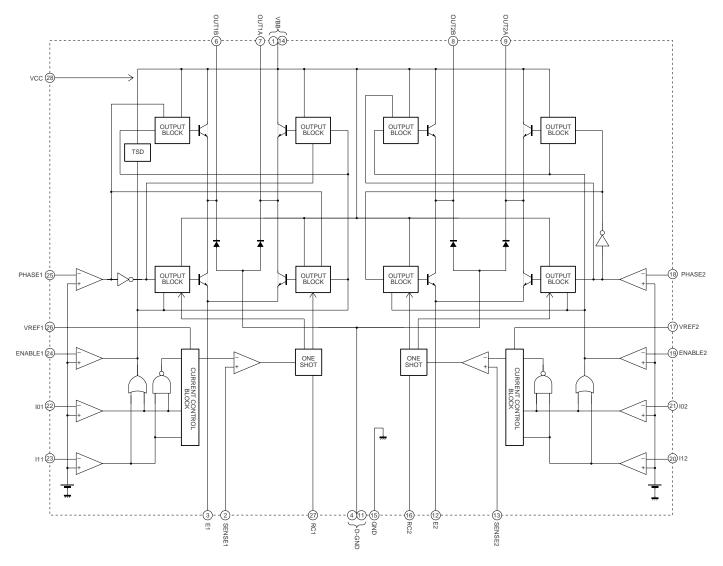

# (8) Gate array (B) block

The block is composed of the gate array (B) and SRAM (2 KByte).

### 1) LR38292(IC10) ... pin-160, QFP (gate array B)

The device has the following functions.

# Printing data process

The image data of the page memory for printing is converted into 400 dpi, and the smoothing and contracting processes are applied.

### 2 Printer (PCU) interface

The control of resetting and so on to PCU and the image data processed in Item ① above are synchronized with the signal (HSYNC) from PCU and are transmitted to PCU in the serial mode.

### ③ DMA controller

- (a) The binary-coded data of the draft transmitted in the serial mode from the gate array (A) LZ9FJ59(IC17) and read with the scanner are transmitted to the page memory.

- (b) The image data which will be printed are read from the page memory, and the process ① is applied to transmit the data to PCU in the serial mode.

### 4 CODEC (HD813201F) interface

- (a) The timing is controlled for CPU to get an access to CODEC.

- (b) The timing is controlled for CODEC to get an access to the page memory.

### ⑤ DRAM controller

Since DRAM is used for the page memory, and the address, RAS and CAS are controlled and refresh-controlled.

### Panel interface

The key input detection on the operation panel, LED lighting control and LCD display control are executed.

# 2) LH5116NA-10 (IC3) -- pin-24, SOP (16-Kbit SRAM)

This SRAM is a line memory for the printing data process (resolution power conversion, smoothening and contracting to 404 dpi) of the gate array (B).

# LR38292 (IC10) Terminal descriptions

| Pin | Name    | I/O      | Function                                 |

|-----|---------|----------|------------------------------------------|

| 20  | VCC     | ., 0     | Power supply                             |

| 62  | VCC     |          | l ower suppry                            |

| 100 | VCC     |          |                                          |

| 142 | VCC     |          |                                          |

| 16  | GND     |          | Ground                                   |

|     |         |          | Ground                                   |

| 21  | GND     |          |                                          |

| 35  | GND     |          |                                          |

| 48  | GND     |          |                                          |

| 61  | GND     |          |                                          |

| 78  | GND     |          |                                          |

| 87  | GND     |          |                                          |

| 101 | GND     |          |                                          |

| 125 | GND     |          |                                          |

| 134 | GND     |          |                                          |

| 143 | GND     |          |                                          |

| 65  | MANRESB | 0        | Manual reset signal                      |

| 66  | RESETB  | ī        | Reset signal                             |

|     |         |          |                                          |

| 89  | A5      | I        | Address signal on the system side        |

| 90  | A4      |          |                                          |

| 91  | A3      |          |                                          |

| 92  | A2      |          |                                          |

| 93  | A1      |          |                                          |

| 70  | D15     | I/O      | Data bus signal on the system side       |

| 71  | D14     |          |                                          |

| 72  | D13     |          |                                          |

| 73  | D12     |          |                                          |

| 74  | D11     |          |                                          |

| 75  | D10     |          |                                          |

| 76  | D10     |          |                                          |

|     |         |          |                                          |

| 77  | D8      |          |                                          |

| 79  | D7      |          |                                          |

| 80  | D6      |          |                                          |

| 81  | D5      |          |                                          |

| 82  | D4      |          |                                          |

| 83  | D3      |          |                                          |

| 84  | D2      |          |                                          |

| 85  | D1      |          |                                          |

| 86  | D0      |          |                                          |

| 88  | CSB     | I        | Chip select signal of gate array LR38292 |

| 97  | RDB     | i        | Read signal on the system bus side       |

| 98  | WRB     | i        | Write signal on the system bus side      |

| 115 | SHCK0B  | 0        | Reversion output of clock (SHCK) from    |

| 113 | SHORUB  | O        | CPU                                      |

| 440 | 011014  |          |                                          |

| 116 | SHCK    | <u> </u> | Clock (19.6 MHz) from CPU                |

| 95  | GAINTB  | 0        | Interrupt request signal to CPU of gate  |

|     |         |          | array LR38292                            |

| 94  | CDCINTB | 0        | Reversion output (to CPU) of interrupt   |

|     |         |          | request signal from HD813201F            |

| 96  | DREQ0B  | 0        | Reversion output (to CPU) of DMA         |

| L   |         |          | transfer request signal from HD813201F   |

| 99  | RSTCDCB | 0        | Reset signal to HD813201F (Default:      |

|     |         |          | Low)                                     |

| 102 | CDCINT  | ı        | Interrupt request signal from HD813201F  |

| 103 | BRQT    |          | Bus right request signal of image bus    |

| .55 | 5       | ,        | from HD813201F                           |

| 104 | BACKB   | 0        | Bus right permission signal of image bus |

| 104 | DAOND   | J        | to HD813201F                             |

| 105 | DBOO    | - 1      |                                          |

| 105 | DRQ0    | I        | DMA transfer request signal from         |

| 100 | DAGUES  |          | HD813201F                                |

| 106 | DACK0B  | 0        | Acknowledge signal of DMA transfer to    |

|     |         |          | HD813201F                                |

| 107 | CSCDCB  | I        | Chip select signal to HD813201F          |

| 108 | MDENB   | I        | Data enable signal of image bus from     |

|     |         |          | HD813201F                                |

| 109 | READY   | 0        | Ready signal of image bus access to      |

|     | '       | -        | HD813201F                                |

| 110 | MAS     | - 1      | Address strobe signal of image bus of    |

| ""  | (0      | •        | HD813201F                                |

|     | 1       |          | 123102011                                |

# LR38292 (IC10) Terminal descriptions

|     | ic to) term |          |                                                 |

|-----|-------------|----------|-------------------------------------------------|

| Pin | Name        | I/O      | Function                                        |

| 111 | MAENB       | - 1      | Address enable signal of image bus of           |

|     |             |          | HD813201F                                       |

| 112 | CK16M       | 1        | 16 MHz clock input                              |

|     |             |          |                                                 |

| 113 | RDCDC       | 0        | Register read signal (active H) of              |

|     |             |          | HD813201F of CPU                                |

| 114 | RDCDCB      | 0        | Register read signal (active L) of              |

|     |             | _        | HD813201F of CPU                                |

| 120 | MA20        | 1        |                                                 |

| 139 |             | 1        | Address of image bus of HD813201F               |

| 138 | MA19        |          |                                                 |

| 137 | MA18        |          |                                                 |

| 136 | MA17        |          |                                                 |

| 135 | MA16        |          |                                                 |

|     |             | 1/0      | A daluage /dete_of :                            |

| 133 | MAD15       | I/O      | Address/data of image bus of                    |

| 132 | MAD14       |          | HD813201F                                       |

| 131 | MAD13       |          | Input mode is selected when                     |

| 130 | MAD12       |          | HD813201F gets an access to image               |

| 129 | MAD11       |          | bus (MAENB=L).                                  |

|     |             |          |                                                 |

| 128 | MAD10       |          | Data bus to memory (page memory) is             |

| 127 | MAD9        |          | selected when gate array LR38292 gets           |

| 126 | MAD8        |          | an access to the image bus.                     |

| 124 | MAD7        |          | Ĭ                                               |

| 123 | MAD6        |          |                                                 |

|     |             |          |                                                 |

| 122 | MAD5        |          |                                                 |

| 121 | MAD4        |          |                                                 |

| 120 | MAD3        |          |                                                 |

| 119 | MAD2        |          |                                                 |

| 118 | MAD1        |          |                                                 |

|     | MAD0        |          |                                                 |

| 117 |             |          |                                                 |

| 155 | DA11        | I/O      | Address bus to memory of image bus              |

| 154 | DA10        |          | (page memory)                                   |

| 153 | DA9         |          | When HD813201F gets an access to the            |

| 152 | DA8         |          | image bus, address of MA21 thru MA16,           |

|     |             |          |                                                 |

| 151 | DA7         |          | MAD15 thru MAD1 are converted to                |

| 150 | DA6         |          | Row/Column address in the page                  |

| 149 | DA5         |          | memory (DRAM) and output.                       |

| 148 | DA4         |          | When gate array LR38292 gets an                 |

| 147 | DA3         |          | access to the image bus, Row/Column             |

| 146 | DA2         |          | address is output to the page memory            |

|     |             |          | ,                                               |

| 145 | DA1         |          | (DRAM).                                         |

| 144 | DA0         |          |                                                 |

| 156 | DWEB        | 0        | Write signal to memory (page memory:            |

|     |             |          | DRAM) of image bus                              |

| 157 | RAS1B       | 0        | RAS1 signal to memory (page memory:             |

| 107 | INACID      |          |                                                 |

|     |             |          | DRAM) of image bus                              |

| 158 | RAS0B       | 0        | RAS0 signal to memory (page memory:             |

|     |             |          | DRAM) of image bus                              |

| 159 | CASB        | 0        | CAS signal to memory (page memory:              |

|     |             |          | DRAM) of image bus                              |

| 140 | DRMSIZE     | 1        | Setting of size of memory (page memory:         |

| 140 | PINIVISIZE  | '        |                                                 |

|     |             |          | DRAM) of image bus                              |

|     |             |          | Low: 16 Mbits                                   |

| L   |             | <u></u>  | High: 12 Mbits                                  |

| 141 | DRMTYPE     | -        | Setting of type of memory (page                 |

|     |             | •        | memory: DRAM) of image bus                      |

|     |             |          | Low: Address 8-bit type                         |

|     |             |          |                                                 |

|     |             |          | High: address 12-bit type                       |

|     |             |          | (Valid only for DRMSIZE=L. Don't care           |

|     |             |          | for DRMSIZE=H.)                                 |

| 67  | STVDB       | 1        | Serial scanner data valid range signal          |

| 68  | SRVID       | i        | Serial scanner data                             |

|     |             |          |                                                 |

| 69  | SCCLK       | <u> </u> | Serial scanner data transfer clock              |

| 51  | PCURESB     | 0        | Reset signal for printer unit                   |

| 52  | HSYNC       | - 1      | Main scanning synchronous signal from           |

|     |             |          | printer unit                                    |

| 53  | EPRDYB      |          | Communication ready signal from printer         |

|     |             | '        | unit                                            |

|     |             |          | JULIIL                                          |

|     | DDD2//5     |          | Data Company of Company 1 1 1 1 1 1 1 1 1 1 1 1 |

| 54  | PRRDYB      | -        | Printing operation ready signal of printer      |

|     | PRRDYB      |          | Printing operation ready signal of printer unit |

|     | PRRDYB      | <br>     | unit                                            |

| 54  |             |          |                                                 |

| Pin | Name         | I/O | Function                                           |

|-----|--------------|-----|----------------------------------------------------|

| 56  | ETBSYB       | I   | Status sending signal of printer unit              |

| 57  | CTBSYB       | 0   | Command sending signal to printer unit             |

| 58  | PRINTB       | 0   | Printing start/continuation signal to printer unit |

| 59  | PDATA        | 0   | Printing image data to printer unit                |

| 60  | CPRDYB       | 0   | Communication ready signal to printer              |

|     |              |     | unit                                               |

| 63  | XIN          | I   | Clock input (quartz oscillator connection)         |

| 64  | XOUT         | 0   | Clock output (quartz oscillator connection)        |

| 38  | LMA10        | 0   | Address bus of line memory for                     |

| 37  | LMA9         |     | smoothing/contracting                              |

| 36  | LMA8         |     |                                                    |

| 34  | LMA7         |     |                                                    |

| 33  | LMA6         |     |                                                    |

| 32  | LMA5         |     |                                                    |

| 31  | LMA4         |     |                                                    |

| 30  | LMA3         |     |                                                    |

| 29  | LMA2         |     |                                                    |

| 28  | LMA1         |     |                                                    |

| 27  | LMA0         |     |                                                    |

| 40  | LMD7         | 0   | Data bus of line memory for                        |

| 41  | LMD6         |     | smoothing/contracting                              |

| 42  | LMD5         |     |                                                    |

| 43  | LMD4         |     |                                                    |

| 44  | LMD3         |     |                                                    |

| 45  | LMD2         |     |                                                    |

| 46  | LMD1         |     |                                                    |

| 47  | LMD0         |     |                                                    |

| 39  | LMWEB        | 1/0 | Octoblidate has and LED and " control              |

| 26  | LD15         | I/O | Control/data bus and LED on/off control            |

| 25  | LD14         |     | signal to key scan and LCD driver on the           |

| 24  | LD13<br>LD12 |     | operation panel                                    |

| 22  | LD12         |     |                                                    |

| 19  | LD10         |     |                                                    |

| 18  | LD10         |     |                                                    |

| 17  | LD9          |     |                                                    |

| 15  | LD7          |     |                                                    |

| 14  | LD6          |     |                                                    |

| 13  | LD5          |     |                                                    |

| 12  | LD4          |     |                                                    |

| 11  | LD3          |     |                                                    |

| 10  | LD2          |     |                                                    |

| 9   | LD1          |     |                                                    |

| 8   | LD0          |     |                                                    |

| 160 | SEN7         | I   | Key input detection signal of operation            |

| 1   | SEN6         |     | panel                                              |

| 2   | SEN5         |     |                                                    |

| 3   | SEN4         |     |                                                    |

| 4   | SEN3         |     |                                                    |

| 5   | SEN2         |     |                                                    |

| 6   | SEN1         |     |                                                    |

| 7   | SEN0         |     |                                                    |

| 49  | MEMTST       | I   | Terminal for device test of integrated             |

|     |              |     | memory                                             |

|     |              | _   | Low is set except in the device test mode.         |

| 50  | TEST         | I   | Terminal for device test                           |

|     |              |     | Low is set except in the device test mode.         |

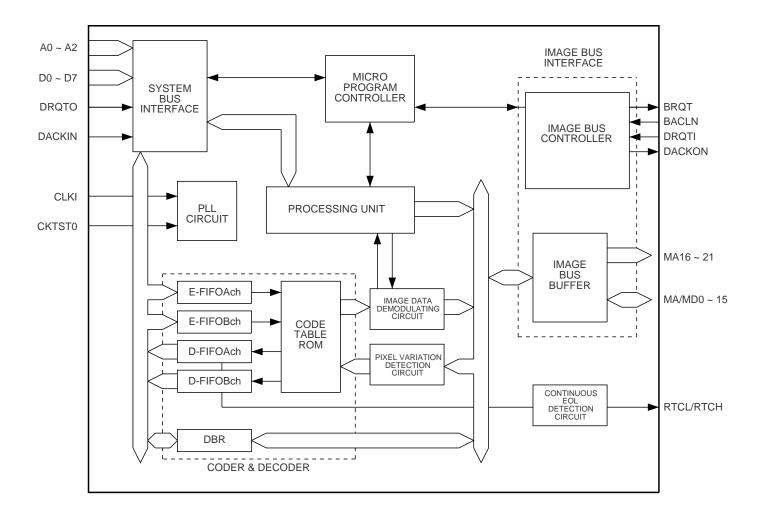

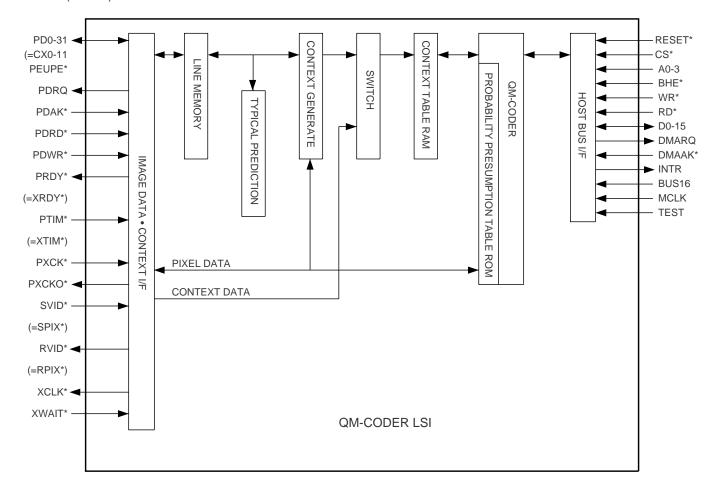

# (9) CODEC block

This block is composed of CODEC, LS374 and LS244 in order to demodulate the contracted image data of the draft read with the scanner and the letter image transmitted in the DMA mode from the system memory.

# 1) HD813201F (IC12) ... pin-80, 6FP (CODEC)

It operates at 16 MHz corresponding to the crystal oscillator (X2) of 16 MHz

The image memory is commonly used as the page memory. The image data of the draft read with the scanner in the page memory is contracted by MMR, and is transferred to the system memory (DRAM: IC16) by the DMA transfer function of CPU. Moreover, the image data transferred in the DMA mode from the system memory are demodulated with MMR, and are developed into the page memory.

# 2) HD74LS374 (IC18) ... pin-20, SOP

The data hold time during writing from main CPU to HD813201F is assured

# 3) HD74LS244 (IC20) ... pin-20, SOP

When the main CPU reads the inner register of HD813201F, it will read the data through this buffer.

Fig. 3

# HD813201F (IC12) Terminal descriptions

| Code  | Terminal No. | I/O                | Function                                                                                                                                                                                                                                                                                                                             |  |  |

|-------|--------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 68/80 | 56           | I                  | If this terminal is at "low" level, it indicates that MPU of system 88 is connected to IDP201. "High" level indicates that MPU of system 80 is connected.                                                                                                                                                                            |  |  |

| A0    | 57           | ı                  | Addresses 0 thru 2 (address terminals). It is connected to the low-order 3 bits of                                                                                                                                                                                                                                                   |  |  |

| A1    | 54           |                    | the system address bus, and MPU is used to get an access to the internal                                                                                                                                                                                                                                                             |  |  |

| A2    | 55           |                    | register of IDP201.                                                                                                                                                                                                                                                                                                                  |  |  |

| D0    | 64           | I/O,               | Data 0 thru 7 (data terminals). They are connected to the system data bus for                                                                                                                                                                                                                                                        |  |  |

| D1    | 62           | Three-state output | bidirectional data transfer between MPU and IDP201. MPU can read and write                                                                                                                                                                                                                                                           |  |  |

| D2    | 65           |                    | the internal register of IDP201.                                                                                                                                                                                                                                                                                                     |  |  |